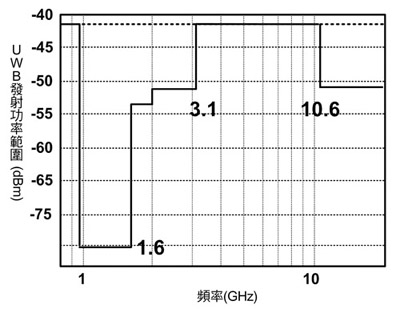

由MB-OFDM聯盟(Multi-band OFDM Alliance, MBOA)提出之標準,超寬頻使用正交分頻多工(Orthogonal Frequency Division Mmultiplexing, OFDM)及跳頻展頻(Frequency Hopping Spread Spectrum, FHSS)等展頻技術,而總共7.5GHz的頻譜則被分為十四個頻段,每一個頻段的頻寬為528MHz,此系統使用了共一百二十二個子載波,並且每個子載波乃使用正交相移調變(Quadrature Phase Shift Keying, QPSK)來調變基頻訊號。

|

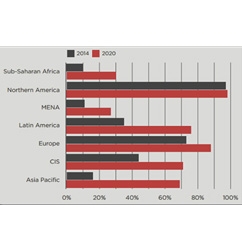

| 圖1 超寬頻發射功率規範 |

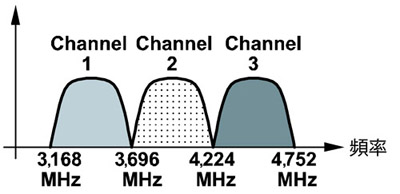

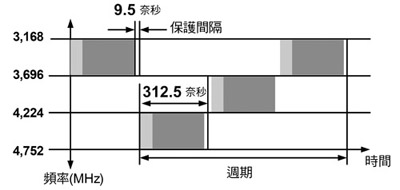

而目前提出的規格可分為兩個模式,模式一使用中心頻率為3,432MHz、3,960MHz及4,488MHz,頻寬為528MHz的三個頻段(圖2);而模式二則除了上述的三個頻段外,增加中心頻率為6,336MHz、6,864MHz、7,392MHz及7,920MHz四個頻段。若以電路設計的複雜度,以及以CMOS電路實現作為考量,只使用三個頻段的模式一具有較高的可行性,因此以下所討論的時脈產生器電路,是針對於模式一頻段之應用,而MB-OFDM UWB系統的頻道切換圖,如圖3所示。

|

| 圖2 MBOA-UWB模式–使用頻段 |

|

| 圖3 頻道切換時域圖 |

每一個正交分頻多工符元(OFDM Symbol)的時間長度為312.5奈秒,其中包含60.6奈秒長的空循環式前置(Null Cyclic Prefix)、242.4奈秒的資料傳輸及9.5奈秒之保護區間(Guard Interval),表示載波頻率須在9.5奈秒間完成切換,這對於頻率合成器的設計上帶來很大的挑戰。

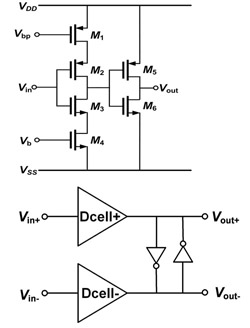

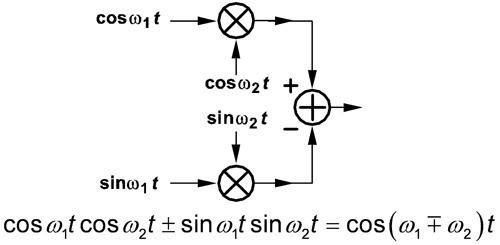

若使用傳統以鎖相迴路(Phase-lock-loop, PLL)為架構的頻率合成器,其鎖定所需要的時間幾乎不可能達到超寬頻系統要求。而目前普遍採用的頻率合成方式是使用單旁波帶混頻器(Single-sideband Mixer, SSB Mixer),如圖4所示,經由控制加法器的正負號,就可合成出所需的頻率,但SSB混頻器的缺點是須使用I/Q的訊號,因此若I/Q訊號有相位差,或是電路不匹配,造成載波漏流或非理想的側頻帶,會將鄰近頻段所傳輸的訊號一起帶進基頻(Baseband),並降低訊雜比(SNR)。且由於此種雜訊是頻帶內的訊號,不易藉由濾波器濾除,因此不採用鎖相迴路同時又具有低頻寬內突波的特性,達成快速切換頻率的功能,是本文時脈產生器電路主要解決的問題。

|

| 圖4 單旁波帶混頻器架構與計算公式 |

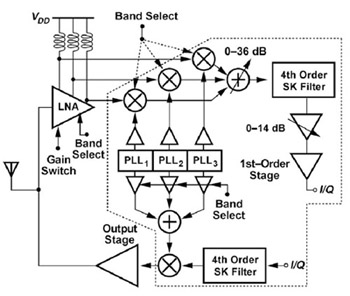

另外也有使用三組固定鎖相迴路進行頻率合成之方法,如圖5所示。其中三組鎖相迴路皆分別輸出固定頻率,並不隨著時間而切換,因此可解決鎖定時間的難題,也避免因單旁頻帶混波器非理想性帶來的問題,不過此方法的缺點為占用較大的晶片面積,較難達成低成本需求。若要同時實現三組鎖相迴路於同一個晶片之中,勢必採用環型振盪器(Ring Oscillator)製作鎖相迴路中之壓控振盪器(VCO),其相位雜訊(Phase Noise)表現較電感-電容振盪器(L-C Oscillator)差,將影響系統效能。而三組鎖相迴路所輸出三組不同頻率的訊號,可能會由基板(Substrate) 或電源線而彼此互相干擾,同樣會產生混附波(Spurious Tone)問題,另外,功率消耗也較高。

|

| 圖5 UWB傳輸機架構圖 |

為解決目前遇到之難題,本文將介紹兩種不同技術,用以產生適用於超寬頻系統之高品質之載波,其一使用延遲鎖定迴路(Delay-locked Loop, DLL)之技術為基礎,另一應用米勒除頻器之技巧。

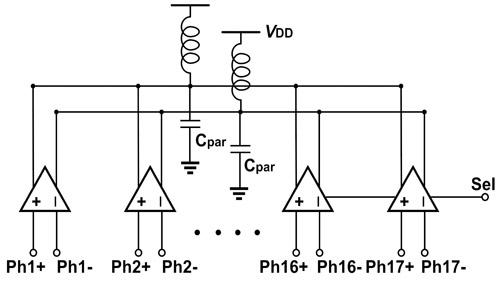

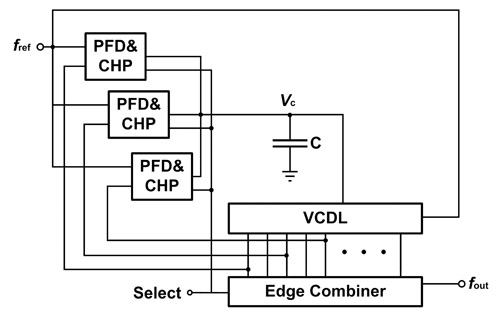

為產生超寬頻系統中需求的三個頻率,本文提出可變延遲單元延遲鎖定迴路(Variable Delay Stage Delay Lock Loop),藉著改變延遲單元的個數,產生不同的輸出頻率,其架構如圖6。經由改變不同回授訊號的來源,等效為改變延遲單元的個數,當迴路再次鎖定時,即產生新的輸出頻率,在此同時,邊緣組合器也須作對應的設定,然而,在切換頻帶時,改變不同延遲單位的輸出,會造成回授訊號上故障(Glitch),使系統誤動作,因此改採用在相位頻率偵測器及電流泵浦進行切換,以解決此問題。

|

| 圖6 可變延遲單元延遲鎖定迴路架構 |

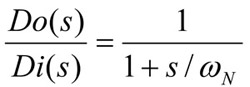

設計應用於超寬頻系統中頻率合成器的最大難題為頻道切換時間須小於9.5奈秒,為符合此需求,首先必須對系統的動態響應加以分析,此系統的轉換函數可表示為:

其中ωN為迴路的頻寬,可表示為:

其中,ICH為電流泵浦的電流,KDL為VCDL的增益,以本設計而言,ωN須夠大以符合頻道切換時間的規格。

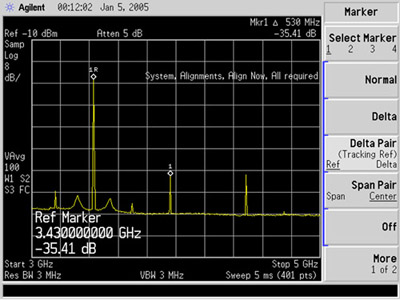

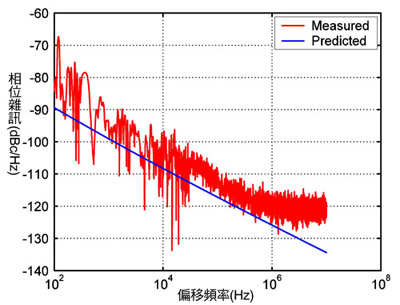

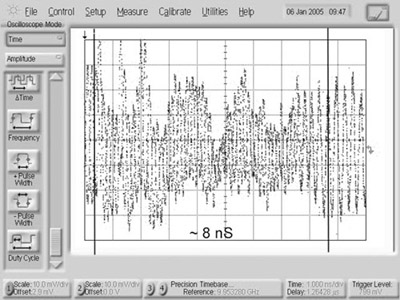

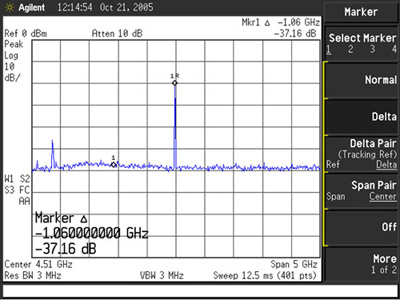

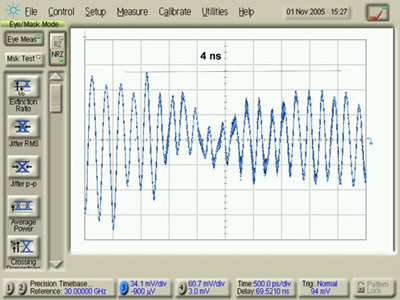

圖12是此頻率合成器的晶片顯微圖,採用互補式金屬氧化物半導體(CMOS)0.18微米製程,晶片的面積為0.98×0.68平方毫米。圖13的頻譜圖是觀察當輸出頻率為3,432MHz的情況下,3,960MHz處的旁頻帶,訊號強度差達35dB,而在528MHz頻段內,沒有明顯的混附波。圖14為輸出頻率為3,432MHz時之相位雜訊圖。在頻率偏差(Frequency Offset)為1MHz處,相位雜訊強度為-120dBc/Hz。圖15則是觀察在輸出頻率切換時之暫態反應,圖中可看出,此電路可以在8奈秒以內完成頻率切換,符合系統規格9.5奈秒的要求,而表1則為頻率合成器的實驗結果。

|

|||||||||||||||||||||||||

以米勒除頻器為基礎 發展時脈產生器

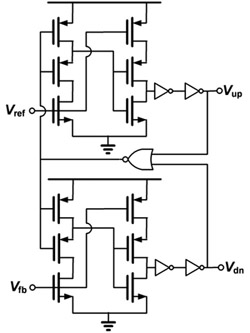

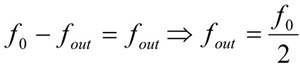

圖16是基本米勒除頻器(Miller Divider)架構,假設混頻器輸出訊號的高階諧波可忽略,則可推導出以下的公式:

|

| 圖16 米勒除頻器架構 |

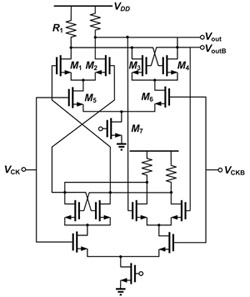

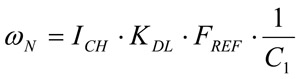

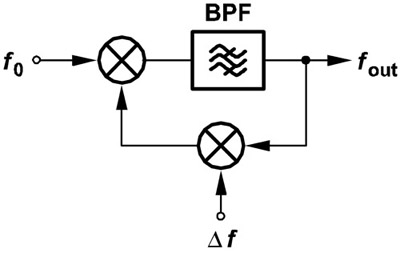

米勒除頻器有著速度快的優點,即使輸入頻率很高也可以正常工作。圖17是本文電路設計採用的架構,在米勒除頻器的回授路徑加上混頻器變形而成。若以類似推導米勒除頻器公式的方法推導,可得出以下的結果:

|

| 圖17 在米勒除頻器的回授路徑加入混頻器 |

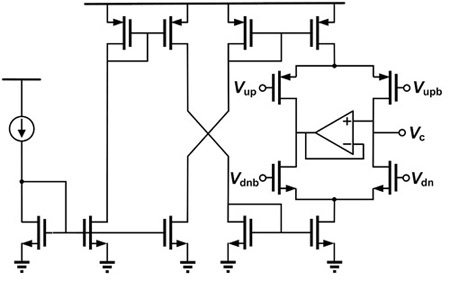

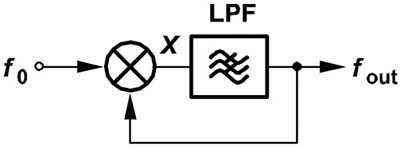

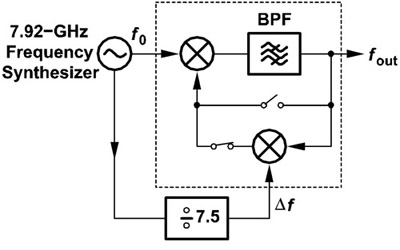

由以上的式子可看出,能穩定存在於這電路的訊號頻率可能有二,一是較高頻率的解(f0+Δf)/2,另一是較低頻率的解(f0-Δf)/2,至於決定輸出頻率為何解的關鍵在於帶通濾波器。只要帶通濾波器的中心頻率較接近(f0+Δf)/2,輸出訊號的頻率就會是(f0+Δf)/2;反之,帶通濾波器的中心頻率較接近(f0-Δf)/2,輸出訊號頻率就為(f0-Δf)/2。因此只要改變帶通濾波器的中心頻率,就可使輸出訊號頻率改變,再加上基本米勒除頻器可產生的除二輸出,一共有三種輸出頻率可供選擇,分別為(f0-Δf)/2、f0/2及(f0+Δf)/2。米勒除頻器本身具有高速的特性,只要帶通濾波器的頻寬夠寬,此電路可符合超寬頻系統的頻率合成器在9.5奈秒內完成頻率的切換之規格,在超寬頻系統應用下,f0為7.92GHz,Δf為1.056GHz,Δf可以經由將f0通過除7.5的除頻器產生(圖18)。

|

| 圖18 可用於超寬頻系統之時脈產生器 |

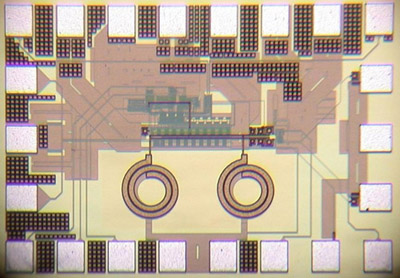

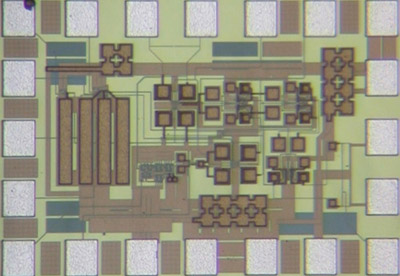

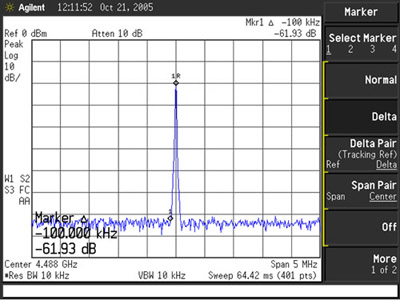

圖19是此時脈產生器的晶片顯微圖,採用CMOS 0.18微米製程,晶片的面積為086×0.66平方毫米。圖20的頻譜圖是觀察當輸出頻率為4,488MHz的情況下其他的載波頻率,如3,960MHz及3,432MHz的訊號強度。距離輸出頻率1.056GHz的地方(3,432MHz),訊號強度差達37dB,而在MBOA-UWB模式一系統所使用頻段內,沒有明顯的混附波。此系統架構最大之混附波,出現在約2GHz以外的地方。

而圖21為圖20頻譜拉近觀察之結果,由圖中可讀出相位雜訊在離中心頻率100kHz約為-101.93dBc/Hz的地方。圖22則是觀察在輸出頻率由3,960MHz切換至4,488MHz的暫態反應。由於由3,960MHz切換至4,488MHz相當於先切斷米勒除頻器的回授路徑,再接上具有混頻器的回授路徑,故在此系統架構下,此種切換情況需要最久的穩定時間,而圖中可以看出,在此種最差的情況下,此電路可在4奈秒以內完成頻率切換,符合系統規格9.5奈秒的要求。

|

本文首先介紹以延遲鎖定迴路為基礎之頻率合成器,利用延遲鎖定迴路可達成高頻寬的特性,再加上切換延時單元數目的設計,能產生適用於超寬頻系統之載波,此系統由0.18微米製程實現,功耗為54毫瓦。另外介紹以米勒除頻器為基本架構的時脈產生器,此時脈產生器可產生應用於超寬頻系統的三個載波頻率,同時達到系統所要求的高速頻帶切換時間,此架構是在傳統米勒除頻器的回授路徑上加上一個混頻器,而輸出頻率則是由帶通濾波器控制,而此時脈產生器已在0.18微米製程中實現,核心電路所消耗功率僅22毫瓦。

(本文作者黃彥筌/蕭耕然就讀於台灣大學電機工程學系研究所,李泰成為台灣大學電機工程學系副教授)